vSyn

vSyn - компилятор языка Си в Verilog. Разработка алгоритмов на языке Си значительно проще, компактней и быстрей, чем на языках описания аппаратуры (Verilog, VHDL, SystemC, etc).

Автоматизированный процесс переноса Си-логики на аппаратный уровень - является весьма эффективным подходом при реализации сложных и больших проектов на PLD (ПЛИС) FPGA:

- Экономия времени на разработку, тестирование и debug-а (код Си гораздо проще отлаживать на х86/64)

- Автоматизированный процесс формирования state-машины (Finite State machine)

- Интерфейс для работы с памятью, совместим с Memory Interface Generator (LogiCORE IP Core от Xilinx)

- Минимизация размера кода и как следствие, уменьшение ошибок

- Возможность не задумываться о сложностях внутренней работы Verilog

- Переносимость кода, возможность использовать пополняемую библиотеку алгоритмов: red-black-tree (std::map)

vSwitch

vSwitch - аппаратное решение для управления пакетами в сети Ethernet 1000/100 Mbit/s. Управление пакетами осуществляется с помощью FPGA, что позволяет работать на скорости канала без потерь пакетов.

- Широкие возможности использования

- Поддержка 100 мегабитных и гигабитных ethernet (1000BASE-TX, 100BASE-TX)

- Низкое энергопотребление (15 ват для 8 гигабитных интерфейсов)

- Идеально подходит для изучения сети Ethernet в домашних условиях

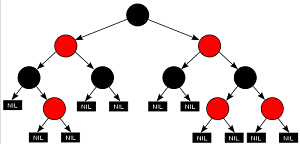

Red-Black-Tree

Красно-чёрное дерево (Red-Black-Tree, RB-Tree) - это алгоритм ассоциативного массива (stl::map). Одно из самобалансирующихся двоичных деревьев поиска, гарантирующих логарифмический рост высоты дерева от числа узлов (N) и быстро выполняющее основные операции дерева поиска: добавление, удаление и поиск узла.

Предложен пример трансляции с помощью vSyn из Си кода в Verilog. Интерфейс совместим с Memory Interface Generator (LogiCORE IP Core от Xilinx) для работы с оперативной памятью.